- Corrélateurs

- Bruits inhérent au numérique : bruit de phase, gigue, stabilité temporelle des circuits numériques

- Compteur à intervalle de temps

- Détection synchrone

- Choix ADC/DAC pour applications TF

- Mesure Sphi(f) et sigma_y(tau)

- Servo controls (Liens fibrés, …)

- Manipulation d'objets et fréquences (atomes froids, spectral hole burning, ions ….)

- Datations « officielles »

- Compteurs, avec et sans temps morts.

- Logiciel / Pilotes

- IP cores (FPGA)

- Chipscope

Outils pour utilisateurs

Outils du site

votre temps local: :: ()

heure officielle (en France) : ::(TZ:)

Heure UTC client: :: Offset client: s - delai: ms - - timeZone: Heure UTC: ::Panneau latéral

fr:nouveau_developpement_2018-_double_dds_8_sorties_pour_piege_rf_programmation_qspi

Ceci est une ancienne révision du document !

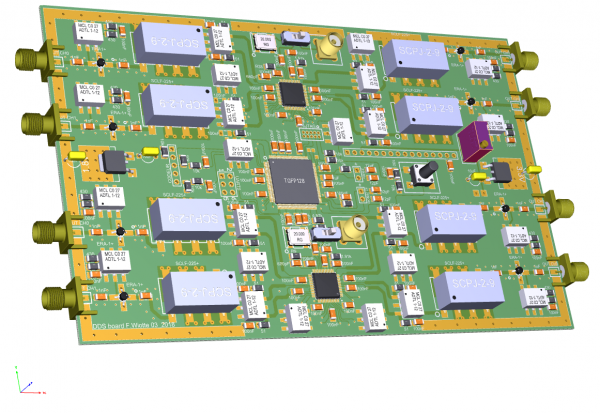

Pour des considérations de vitesse d’exécution et de chargement des données nous avons fait évoluer les cartes DDS pour l'expérience BEC du LPL. La programmation des DDS est réalisé en Quad SPI à une vitesse de 60MHz. les données sont transmises au uC (ARM 120MHz) grâce à l'interface USB-UART non représentée sur le PCB ci-dessous à une vitesse de 10Mbps.

fr/nouveau_developpement_2018-_double_dds_8_sorties_pour_piege_rf_programmation_qspi.1523004318.txt.gz · Dernière modification: 2018/04/06 10:45 par fwiotte

Outils de la page

Sauf mention contraire, le contenu de ce wiki est placé sous les termes de la licence suivante : CC Attribution-Share Alike 4.0 International