- Corrélateurs

- Bruits inhérent au numérique : bruit de phase, gigue, stabilité temporelle des circuits numériques

- Compteur à intervalle de temps

- Détection synchrone

- Choix ADC/DAC pour applications TF

- Mesure Sphi(f) et sigma_y(tau)

- Servo controls (Liens fibrés, …)

- Manipulation d'objets et fréquences (atomes froids, spectral hole burning, ions ….)

- Datations « officielles »

- Compteurs, avec et sans temps morts.

- Logiciel / Pilotes

- IP cores (FPGA)

- Chipscope

Outils pour utilisateurs

Outils du site

votre temps local: :: ()

heure officielle (en France) : ::(TZ:)

Heure UTC client: :: Offset client: s - delai: ms - - timeZone: Heure UTC: ::Panneau latéral

fr:nouveau_developpement_2018-_double_dds_8_sorties_pour_piege_rf_programmation_qspi

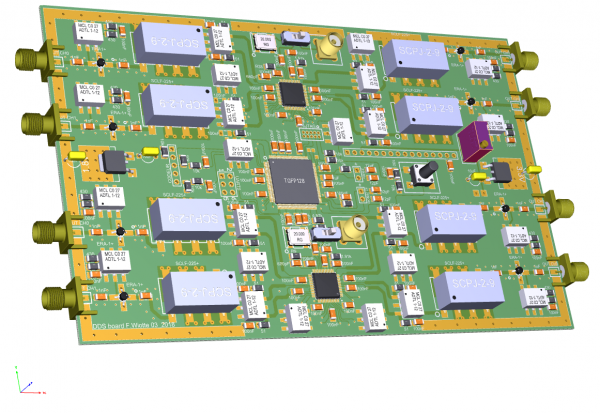

Pour des considérations de vitesse d’exécution et de chargement des données nous avons fait évoluer les cartes DDS pour l'expérience BEC du LPL. La programmation des DDS est réalisé en Quad SPI à une vitesse de 60MHz. les données sont transmises au uC (ARM 120MHz) grâce à l'interface USB-UART non représentée sur le PCB ci-dessous à une vitesse de 10Mbps.

Code C présentant les routines principales avec IAR Workbench for ARM

Wiotte Fabrice

Ingénieur d'étude CNRS

Service Electronique D002 Rdc

CNRS – URM7538 – Université Paris 13

99 Avenue J.-B. Clément

93430 Villetaneuse

http://www-lpl.univ-paris13.fr/

This is part of revision 2.1.0.12573 of the EK-TM4C1294XL Firmware Package.

void init_SPI1_mode_quad_bit(void)

{

// Enable Peripheral SSI1

//if Quad SPI

//***********************//

//GPIO_PE4_SSI1XDAT0 <= BIT 4 BIT 0 only need 2 CLK cycle to send 8bits.

//GPIO_PE5_SSI1XDAT1 <= BIT 5 BIT 1 only need 2 CLK cycle to send 8bits.

//GPIO_PD4_SSI1XDAT2 <= BIT 6 BIT 2 only need 2 CLK cycle to send 8bits.

//GPIO_PD5_SSI1XDAT3 <= BIT 7 BIT 3 only need 2 CLK cycle to send 8bits.

//*************************************//

//Polarity Phase Mode

// 0 0 SSI_FRF_MOTO_MODE_0

// 0 1 SSI_FRF_MOTO_MODE_1

// 1 0 SSI_FRF_MOTO_MODE_2

// 1 1 SSI_FRF_MOTO_MODE_3

//*************************************//

//************************//

// SSI1 is used with the following GPIO Pin Mapping

// SSI1CLK : PB5

// SSI1FSS : PB4

// SSI1XDAT0 : PE4

// SSI1XDAT1 : PE5

// SSI1XDAT2 : PD4

// SSI1XDAT3 : PD5

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOB);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOD);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOE);

SysCtlPeripheralEnable(SYSCTL_PERIPH_SSI1);

// Configure the pin muxing for SSI1 functions on port B4, B5, E4, E5,D4, D5

GPIOPinConfigure(GPIO_PB5_SSI1CLK);

GPIOPinConfigure(GPIO_PB4_SSI1FSS);

GPIOPinConfigure(GPIO_PE4_SSI1XDAT0);

GPIOPinConfigure(GPIO_PE5_SSI1XDAT1);

GPIOPinConfigure(GPIO_PD4_SSI1XDAT2);

GPIOPinConfigure(GPIO_PD5_SSI1XDAT3);

/* Configure pad settings */

GPIOPadConfigSet(GPIO_PORTB_BASE, GPIO_PIN_5|GPIO_PIN_4, GPIO_STRENGTH_12MA, GPIO_PIN_TYPE_STD);

GPIOPadConfigSet(GPIO_PORTE_BASE, GPIO_PIN_5|GPIO_PIN_4, GPIO_STRENGTH_12MA, GPIO_PIN_TYPE_STD);

GPIOPadConfigSet(GPIO_PORTD_BASE, GPIO_PIN_5|GPIO_PIN_4, GPIO_STRENGTH_12MA, GPIO_PIN_TYPE_STD);

// Configure the GPIO settings for the SSI pins. This function also gives

// control of these pins to the SSI hardware.

GPIOPinTypeSSI(GPIO_PORTB_BASE,GPIO_PIN_5|GPIO_PIN_4);

GPIOPinTypeSSI(GPIO_PORTE_BASE,GPIO_PIN_5|GPIO_PIN_4);

GPIOPinTypeSSI(GPIO_PORTD_BASE,GPIO_PIN_5|GPIO_PIN_4);

SSIConfigSetExpClk(SSI1_BASE, 120000000, SSI_FRF_MOTO_MODE_0, SSI_MODE_MASTER, 60000000, 8);

//

// Enable the SSI1 module.

//

SSI1_CR1_R = 0x00000080;

SSIEnable(SSI1_BASE);

}

void init_SPI0_mode_quad_bit(void)

{

// Enable Peripheral SSI0

//if Quad SPI

//***********************//

//***********************//

//GPIO_PA4_SSI0XDAT0 <= BIT 4 BIT 0 only need 2 CLK cycle to send 8bits.

//GPIO_PA5_SSI0XDAT1 <= BIT 5 BIT 1 only need 2 CLK cycle to send 8bits.

//GPIO_PA6_SSI0XDAT2 <= BIT 6 BIT 2 only need 2 CLK cycle to send 8bits.

//GPIO_PA7_SSI0XDAT3 <= BIT 7 BIT 3 only need 2 CLK cycle to send 8bits.

//************************//

//*************************************//

//Polarity Phase Mode

// 0 0 SSI_FRF_MOTO_MODE_0

// 0 1 SSI_FRF_MOTO_MODE_1

// 1 0 SSI_FRF_MOTO_MODE_2

// 1 1 SSI_FRF_MOTO_MODE_3

//*************************************//

//************************//

// SSI1 is used with the following GPIO Pin Mapping

// SSI0CLK : PA2

// SSI0FSS : PA3

// SSI0XDAT0 : PA4

// SSI0XDAT1 : PA5

// SSI0XDAT2 : PA6

// SSI0XDAT3 : PA7

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOA);

SysCtlPeripheralEnable(SYSCTL_PERIPH_SSI0);

// Configure the pin muxing for SSI0 functions on port A2, A3, A4, A5, A6, A7

GPIOPinConfigure(GPIO_PA2_SSI0CLK);

GPIOPinConfigure(GPIO_PA3_SSI0FSS);

GPIOPinConfigure(GPIO_PA4_SSI0XDAT0);

GPIOPinConfigure(GPIO_PA5_SSI0XDAT1);

GPIOPinConfigure(GPIO_PA6_SSI0XDAT2);

GPIOPinConfigure(GPIO_PA7_SSI0XDAT3);

/* Configure pad settings */

GPIOPadConfigSet(GPIO_PORTA_BASE, GPIO_PIN_2|GPIO_PIN_3, GPIO_STRENGTH_12MA, GPIO_PIN_TYPE_STD);

GPIOPadConfigSet(GPIO_PORTA_BASE, GPIO_PIN_4|GPIO_PIN_5, GPIO_STRENGTH_12MA, GPIO_PIN_TYPE_STD);

GPIOPadConfigSet(GPIO_PORTA_BASE, GPIO_PIN_6|GPIO_PIN_7, GPIO_STRENGTH_12MA, GPIO_PIN_TYPE_STD);

// Configure the GPIO settings for the SSI pins. This function also gives

// control of these pins to the SSI hardware.

GPIOPinTypeSSI(GPIO_PORTA_BASE,GPIO_PIN_2|GPIO_PIN_3);

GPIOPinTypeSSI(GPIO_PORTA_BASE,GPIO_PIN_4|GPIO_PIN_5);

GPIOPinTypeSSI(GPIO_PORTA_BASE,GPIO_PIN_6|GPIO_PIN_7);

SSIConfigSetExpClk(SSI0_BASE, 120000000, SSI_FRF_MOTO_MODE_0, SSI_MODE_MASTER, 60000000, 8);

SSIAdvModeSet(SSI0_BASE, SSI_ADV_MODE_WRITE);

SSIAdvModeSet(SSI0_BASE,SSI_ADV_MODE_BI_WRITE);

//

// Enable the SSI0 module.

//

SSI0_CR1_R = 0x00000080;

SSIEnable(SSI0_BASE);

}

void init_SPI0_mode_single_bit(void)

{

// Enable Peripheral SSI0

//if Single bit serial mode SPI

//***********************//

// SSI0 is used with the following GPIO Pin Mapping

// SSI1CLK : PA2

// SSI1FSS : PA3

// SSI1XDAT0 : PA4

//************************//

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOA);

SysCtlPeripheralEnable(SYSCTL_PERIPH_SSI0);

GPIOPinConfigure(GPIO_PA2_SSI0CLK);

GPIOPinConfigure(GPIO_PA3_SSI0FSS);

GPIOPinConfigure(GPIO_PA4_SSI0XDAT0);

// Configure the GPIO settings for the SSI pins. This function also gives

// control of these pins to the SSI hardware.

GPIOPinTypeSSI(GPIO_PORTA_BASE,GPIO_PIN_2|GPIO_PIN_3|GPIO_PIN_4);

SSIConfigSetExpClk(SSI0_BASE, 120000000, SSI_FRF_MOTO_MODE_0, SSI_MODE_MASTER, 60000000, 8);

//

// Enable the SSI0 module.

//

SSI0_CR1_R = 0x00000000;

SSIEnable(SSI0_BASE); // Enable the SSI

}

void init_SPI1_mode_single_bit(void)

{

// Enable Peripheral SSI1

//if Single bit serial mode SPI

//***********************//

// SSI1 is used with the following GPIO Pin Mapping

// SSI1CLK : PB5

// SSI1FSS : PB4

// SSI1XDAT0 : PE4

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOB);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOE);

SysCtlPeripheralEnable(SYSCTL_PERIPH_SSI1);

// Configure the pin muxing for SSI1 functions on port B4, B5, E4,

GPIOPinConfigure(GPIO_PB5_SSI1CLK);

GPIOPinConfigure(GPIO_PB4_SSI1FSS);

GPIOPinConfigure(GPIO_PE4_SSI1XDAT0);

// Configure the GPIO settings for the SSI pins. This function also gives

// control of these pins to the SSI hardware.

GPIOPinTypeSSI(GPIO_PORTB_BASE,GPIO_PIN_5|GPIO_PIN_4);

GPIOPinTypeSSI(GPIO_PORTE_BASE,GPIO_PIN_4);

SSIConfigSetExpClk(SSI1_BASE, 120000000, SSI_FRF_MOTO_MODE_0, SSI_MODE_MASTER, 60000000, 8);

//

// Enable the SSI1 module.

//

SSI1_CR1_R = 0x00000000;

SSIEnable(SSI1_BASE);

}

// init data transfert SPI data to send SSI0

void ssi0PutData( int instruction,long data,int num_byte)

{

int i=0;

SSI0_DR_R = instruction;

while( num_byte )

{

SSI0_DR_R = data >>(num_byte-1-i)*8;

num_byte--;

}

while( !( SSI0_SR_R & SSI_SR_TNF ) )

{

;

}

}

// init data transfert SPI data to send SSI1

void ssi1PutData( int instruction,long data,int num_byte)

{

int i=0;

SSI1_DR_R = instruction;

while( num_byte )

{

SSI1_DR_R = data >>(num_byte-1-i)*8;

num_byte--;

}

while( !( SSI1_SR_R & SSI_SR_TNF ) )

{

;

}

}

void PortH_Init(void) //// Initialize GPIO Port H

{

// activate clock for Port H

SYSCTL_RCGCGPIO_R |= SYSCTL_RCGCGPIO_R7;

// allow time for clock to stabilize

while((SYSCTL_PRGPIO_R&SYSCTL_PRGPIO_R7) == 0){};

GPIO_PORTH_DIR_R = 0x0F; // make PH3-0 out

GPIO_PORTH_AFSEL_R &= ~0x0F; // disable alt funct on PH3-0

//GPIO_PORTH_PUR_R = 0x03; // enable pull-up on

GPIO_PORTH_DEN_R = 0x0F; // enable digital I/O on PH3-0

GPIO_PORTH_PCTL_R &= ~0x0000FFFF; // 4) configure PH3-0 as GPIO

//GPIO_PORTH_AMSEL_R = 0; // disable analog functionality on PH3-0

}

void PortD_Init(void) //// Initialize GPIO Port D

{

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOD);

// activate clock for Port H

SYSCTL_RCGCGPIO_R = SYSCTL_RCGCGPIO_R3; // activate clock for Port D

// allow time for clock to stabilize

while((SYSCTL_PRGPIO_R&SYSCTL_PRGPIO_R3) == 0){};

HWREG(GPIO_PORTD_BASE + GPIO_O_LOCK) = GPIO_LOCK_KEY;

HWREG(GPIO_PORTD_BASE + GPIO_O_CR) = 0x80;

GPIO_PORTD_DIR_R |= 0xFF; // make PD7-0 out

//GPIO_PORTD_AFSEL_R &= ~0x0F; // disable alt funct on PD7-0

//GPIO_PORTD_PUR_R = 0x03; // enable pull-up on

GPIO_PORTD_DEN_R |= 0xFF; // enable digital I/O on PD7-0

GPIO_PORTD_PCTL_R &= ~0xFFFFFFFF; // 4) configure PD7-0 as GPIO

//GPIO_PORTH_AMSEL_R = 0; // disable analog functionality on PD7-0

}

void PortN_Init(void)

{

// activate clock for Port N

SYSCTL_RCGCGPIO_R |= SYSCTL_RCGCGPIO_R12;

// allow time for clock to stabilize

while((SYSCTL_PRGPIO_R&SYSCTL_PRGPIO_R12) == 0){};

GPIO_PORTN_DIR_R |= 0x3F; // make PN5-0 out

GPIO_PORTN_AFSEL_R &= ~0x3F; // disable alt funct on PN5-0

GPIO_PORTN_DEN_R |= 0x3F; // enable digital I/O on PN5-0

// configure PN3-0 as GPIO

GPIO_PORTN_PCTL_R &= ~0xFFFFFFFF; // 4) configure PN7-0 as GPIO

GPIO_PORTN_AMSEL_R &= ~0x3F; // disable analog functionality on PN5-0

}

void PortA_Init(void)

{

// activate clock for Port A

SYSCTL_RCGCGPIO_R |= SYSCTL_RCGCGPIO_R0;

// allow time for clock to stabilize

while((SYSCTL_PRGPIO_R&SYSCTL_PRGPIO_R0) == 0){};

GPIO_PORTA_DIR_R |= 0xC0; // make PA6,7 out

//GPIO_PORTA_AFSEL_R &= ~0xFF; // disable alt funct on PA7-0

GPIO_PORTA_DEN_R |= 0xFF; // enable digital I/O on PA7-0

// configure PA7-0 as GPIO

//GPIO_PORTA_PCTL_R &= ~0xFFFFFFFF; // 4) configure PA7-0 as GPIO

GPIO_PORTA_AMSEL_R &= ~0xFF; // disable analog functionality on PA7-0

}

void PeripheralEnableInit(void)

{

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOA);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOB);

//SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOC);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOD);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOE);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOH);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPION);

//SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOF);

}

int main(void)

{

// clock to 120MHz

ui32SysClkFreq = SysCtlClockFreqSet((SYSCTL_XTAL_25MHZ | SYSCTL_OSC_MAIN | SYSCTL_USE_PLL | SYSCTL_CFG_VCO_480),

120000000);

volatile uint32_t ui32Loop;

PeripheralEnableInit();

PortA_Init();

PortD_Init();

PortH_Init();

PortN_Init();

//Enable Peripheral SSI0 single bit SPI

init_SPI0_mode_single_bit();

// make master reset DDS2

PN1 = 0x02; // reset DDS2

SysCtlDelay(200);

PN1 = 0x00;

// data send to SPI0 PORT @60Mbs to two DDS card

ssi0PutData(FR1_ADRESS,FR1,FR1_NUM_BYTE);

ssi0PutData(CSR_ADRESS,0xF0,CSR_NUM_BYTE); //select CH0 and CH1 and CH2 and CH3

ssi0PutData(FTW_ADRESS,0x10624DD,FTW_NUM_BYTE);

ssi0PutData(CSR_ADRESS,0xF6,CSR_NUM_BYTE); //AD9959 CH0 CH1 MSB first 4-bit serial mode

SysCtlDelay(100);

PN0 = 0x01; // AD9959 I/O update

SysCtlDelay(20);

PN0 = 0x00;

//Enable Peripheral SSI0 quad SPI

init_SPI0_mode_quad_bit();

ssi0PutData(FTW_ADRESS,0x51EB851,FTW_NUM_BYTE);

SysCtlDelay(100);

PN0 = 0x01; // AD9959 I/O update

SysCtlDelay(20);

PN0 = 0x00;

//Enable Peripheral SSI1 single bit SPI

init_SPI1_mode_single_bit();

// make master reset DDS1

PN4 = 0x10; // reset DDS1

SysCtlDelay(200);

PN4 = 0x00;

// data send to SPI1 PORT @60Mbs to two DDS card

ssi1PutData(FR1_ADRESS,FR1,FR1_NUM_BYTE);

ssi1PutData(CSR_ADRESS,0xF0,CSR_NUM_BYTE); //select CH0 and CH1 and CH2 and CH3

ssi1PutData(FTW_ADRESS,0x10624DD,FTW_NUM_BYTE);

ssi1PutData(CSR_ADRESS,0xF6,CSR_NUM_BYTE); //AD9959 CH0 CH1 MSB first 4-bit serial mode

SysCtlDelay(100);

PN3 = 0x08; // AD9959 I/O update

SysCtlDelay(20);

PN3 = 0x00;

//Enable Peripheral SSI1 quad SPI

init_SPI1_mode_quad_bit();

ssi1PutData(FTW_ADRESS,0x51EB851,FTW_NUM_BYTE);

SysCtlDelay(100);

PN3 = 0x08; // AD9959 I/O update

SysCtlDelay(20);

PN3 = 0x00;

}

fr/nouveau_developpement_2018-_double_dds_8_sorties_pour_piege_rf_programmation_qspi.txt · Dernière modification: 2018/04/06 14:05 par fwiotte

Outils de la page

Sauf mention contraire, le contenu de ce wiki est placé sous les termes de la licence suivante : CC Attribution-Share Alike 4.0 International